#### **EMBEDDED SYSTEMS** BASED ON CORTEX-M4 AND THE RENESAS SYNERGY PLATFORM

2020 PROF. DOUGLAS RENAUX, PHD PROF. ROBSON LINHARES, DR. UTFPR / ESYSTECH

RENESAS ELECTRONICS CORPORATION

BIG IDEAS FOR EVERY SPACE RENESAS

# **6 – INTERRUPT CONTROLLER**

- NVIC

- Structure

- Registers

- CMSIS interface for NVIC operations

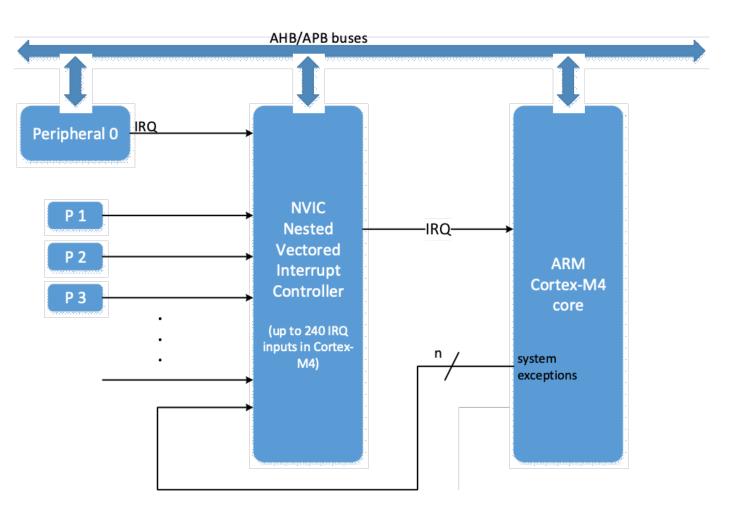

The Nested Vectored Interrupt Controller (NVIC) is an integral part of the Cortex-M4 architecture. Hence, all Cortex-M4 have the same interrupt controller.

Exception handling was examined in Section 3 (link)

Functionality of the NVIC:

- Detect interrupt requests (IRQ) at its inputs and combine them into a single interrupt request to the microprocessor core

- Capability to mask any given input

- Associate inputs to interrupt priority levels

#### NVIC

The Cortex-M4 NVIC may have up to 240 IRQ inputs.

Each input is an interrupt request coming from an integrated peripheral, an external pin, or even from the core itself to inform of a system exception.

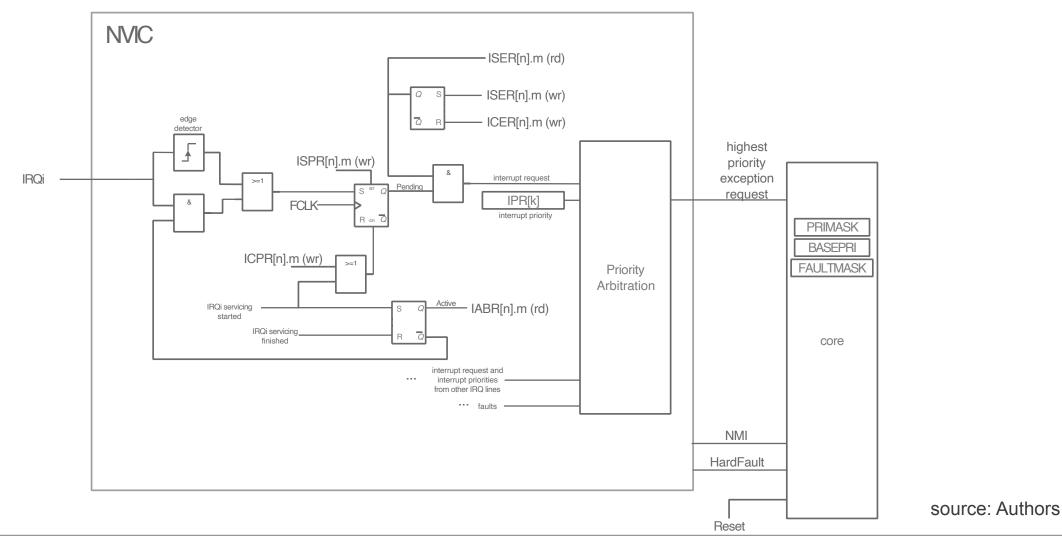

The operation of the NVIC is configured by the core via a set of NVIC registers that provide the functionality of:

- input masking

- IRQ priority assignment

- check status of input (is there a pending IRQ?)

source: Authors

#### **NVIC CHARACTERISTICS**

The Nested Vectored Interrupt Controller provides support for:

- Nested exceptions each exception has an associated priority level. Nesting means that when an exception is being serviced, it can be interrupted by a higher priority exception that was activated. Once the higher priority exception has its service completed, the lower priority service resumes.

- Vectored exceptions the starting addresses of the service routines (handlers) are stored in a table (vector table). When

IRQi is detected the processor simply reads entry i of the table and starts servicing, avoiding delays to start the handler.

- Interrupt masking each IRQi can be individually masked, i.e. ignored.

### **VECTOR TABLE**

By default, its start address is 0x0.

The table has a 31-bit address for each of the possible exceptions (number is implementation dependent).

The 32th bit (the LSb) is used to identify the instruction set (ARM or Thumb) and must be always set in a Cortex-M processor

The first entry in the table is the initial value of the SP.

The next 15 entries are for the system exceptions (Reset, NMI, ... SysTick).

Then follow up to 240 entries for IRQ0 to IRQ239.

# **VECTOR TABLE FOR THE RENESAS S7G2**

On the S7G2 the interrupt sources are managed by the ICU – Interrupt Control Unit.

The ICU sits between the peripherals and the NVIC, preprocessing the interrupt requests before sending them to the NVIC.

| Table 14.3          | Interrupt vector table (1/3) |               |             |                                                      |  |  |  |

|---------------------|------------------------------|---------------|-------------|------------------------------------------------------|--|--|--|

| Exception<br>number | IRQ number                   | Vector offset | Source      | Description                                          |  |  |  |

| 0                   | -                            | 000h          | ARM         | Initial stack pointer                                |  |  |  |

| 1                   | -                            | 004h          | ARM         | Initial program counter (Reset Vector)               |  |  |  |

| 2                   | -                            | 008h          | ARM         | Non-maskable interrupt (NMI)                         |  |  |  |

| 3                   | -                            | 00Ch          | ARM         | Hard fault                                           |  |  |  |

| 4                   | -                            | 010h          | ARM         | MemManage fault                                      |  |  |  |

| 5                   | -                            | 014h          | ARM         | Bus fault                                            |  |  |  |

| 6                   | -                            | 018h          | ARM         | Usage fault                                          |  |  |  |

| 7                   | -                            | 01Ch          | ARM         | Reserved                                             |  |  |  |

| 8                   | -                            | 020h          | ARM         | Reserved                                             |  |  |  |

| 9                   | _                            | 024h          | ARM         | Reserved                                             |  |  |  |

| 10                  | -                            | 028h          | ARM         | Reserved                                             |  |  |  |

| 11                  | -                            | 02Ch          | ARM         | Supervisor call (SVCall)                             |  |  |  |

| 12                  | -                            | 030h          | ARM         | Debug Monitor                                        |  |  |  |

| 13                  | -                            | 034h          | ARM         | Reserved                                             |  |  |  |

| 14                  | -                            | 038h          | ARM         | Pendable request for system service (PendableSrvReq) |  |  |  |

| 15                  | -                            | 03Ch          | ARM         | System tick timer (SysTick)                          |  |  |  |

| 16                  | 0                            | 040h          | ICU.IELSR0  | Event selected in the ICU.IELSR0 register            |  |  |  |

| 17                  | 1                            | 044h          | ICU.IELSR1  | Event selected in the ICU.IELSR1 register            |  |  |  |

| 18                  | 2                            | 048h          | ICU.IELSR2  | Event selected in the ICU.IELSR2 register            |  |  |  |

| 19                  | 3                            | 04Ch          | ICU.IELSR3  | Event selected in the ICU.IELSR3 register            |  |  |  |

|                     |                              |               |             |                                                      |  |  |  |

| 107                 | 91                           | 1ACh          | ICU.IELSR91 | Event selected in the ICU.IELSR91 register           |  |  |  |

| 108                 | 92                           | 1B0h          | ICU.IELSR92 | Event selected in the ICU.IELSR92 register           |  |  |  |

| 109                 | 93                           | 1B4h          | ICU.IELSR93 | Event selected in the ICU.IELSR93 register           |  |  |  |

| 110                 | 94                           | 1B8h          | ICU.IELSR94 | Event selected in the ICU.IELSR94 register           |  |  |  |

| 111                 | 95                           | 1BCh          | ICU.IELSR95 | Event selected in the ICU.IELSR95 register           |  |  |  |

|                     |                              |               |             |                                                      |  |  |  |

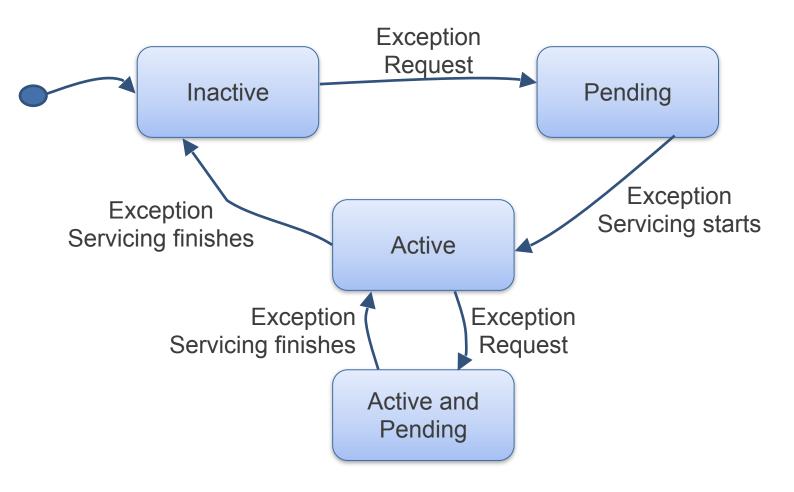

# **EXCEPTION HANDLING STATE MACHINE**

source: Authors

### FUNCTIONAL MODEL OF THE NVIC

BIG IDEAS FOR EVERY SPACE RENESAS

#### **NVIC – ARM DOCUMENTATION**

- ARMv7-M Architecture Reference Manual (2014)

<u>ARM DDI 0403E.b</u>

- ARM® Cortex® -M4 Processor Revision: r0p1 (2015)

Technical Reference Manual

<u>ARM 100166\_0001\_00\_en</u>

- Cortex<sup>™</sup>-M4 Devices Generic User Guide (2011)

<u>ARM DUI 0553A</u>

#### Table 6-1 NVIC registers

| Address                 | Name                    | Туре | Reset      | Description                              |

|-------------------------|-------------------------|------|------------|------------------------------------------|

| 0xE000E004              | ICTR                    | RO   | -          | Interrupt Controller Type Register, ICTR |

| 0xE000E100 - 0xE000E11C | NVIC_ISER0 - NVIC_ISER7 | RW   | 0x00000000 | Interrupt Set-Enable Registers           |

| 0xE000E180 - 0xE000E19C | NVIC_ICER0 - NVIC_ICER7 | RW   | 0x00000000 | Interrupt Clear-Enable Registers         |

| 0xE000E200 - 0xE000E21C | NVIC_ISPR0 - NVIC_ISPR7 | RW   | 0x00000000 | Interrupt Set-Pending Registers          |

| 0xE000E280- 0xE000E29C  | NVIC_ICPR0 - NVIC_ICPR7 | RW   | 0x00000000 | Interrupt Clear-Pending Registers        |

| 0xE000E300 - 0xE000E31C | NVIC_IABR0 - NVIC_IABR7 | RO   | 0x00000000 | Interrupt Active Bit Register            |

| 0xE000E400- 0xE000E4EC  | NVIC_IPR0 - NVIC_IPR59  | RW   | 0x00000000 | Interrupt Priority Register              |

source: ARM® Cortex® -M4 Technical Reference Manual

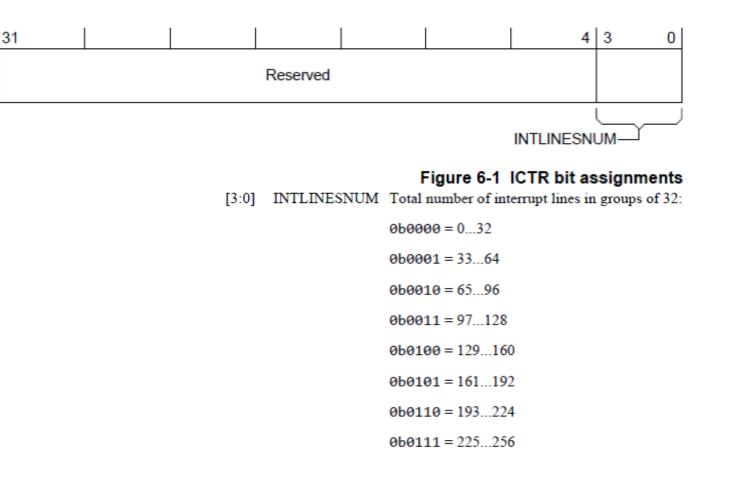

### **NVIC REGISTERS – ICTR**

Since the number of input lines (IRQi) to the NVIC is implementation dependent, so is the number of registers to control the NVIC.

ICTR informs how many control registers are actually implemented in any given NVIC.

For the Renesas S7G2,

ICTR.INTLINESNUM holds the value 2, meaning that there are 3 registers of each type (ISER, ICER, ISPR, ICPR, IABR, with indexes 0..2; and 24 registers IPR, with indexes 0..23). The number of input lines IRQi on this processor is limited to 96.

source: ARM® Cortex® -M4 Technical Reference Manual

**BIG IDEAS FOR EVERY SP**

**I**

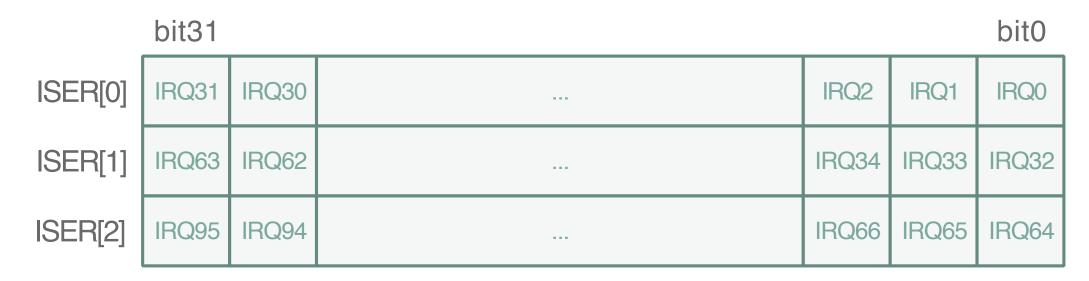

#### **NVIC REGISTERS – ISER – S7G2**

In a Renesas S7G2, each bit of registers ISER[0] to ISER[2] corresponds to one of the 96 IRQi lines.

on write: 1 enables the interrupt line, 0 has no effect

on read: returns the current state of each IRQi line

0 = disabled, 1 = enabled

#### NVIC REGISTERS – ICER/ISPR/ICPR/IABR – S7G2

Same bit assignment as for ISER.

ICER: on write: 1 disables the interrupt line, 0 has no effect

on read: report the current state of each IRQi line, 0 = disabled, 1 = enabled

ISPR: on write: 1 sets the interrupt line to **pending**, 0 has no effect

on read: report the current state of each IRQi line, 0 = not-pending, 1 = pending

ICPR: on write: 1 clears the pending state of the interrupt line, 0 has no effect

on read: report the current state of each IRQi line, 0 = not-pending, 1 = pending

IABR: read only: report the current state of each IRQi line, 0 = not-active, 1 = active

### **NVIC PRIORITIES**

On the Cortex-M4, each IRQi line has a register that defines its priority level in relation to the other IRQi lines. This register may have up to 8 bits (implementation defined).

On the S7G2, 4-bit registers are implemented, allowing the definition of up to 16 priority levels. 0 is the highest priority and 15 is the lowest. Since these bits are left aligned, the actual values are 0, 0x10, 0x20, 0x30, ... 0xF0.

A higher priority interrupt preempts a lower priority interrupt whose handler is being executed.

#### **NVIC PRIORITIES**

The bits of the priority register are divided into:

- Priority Group

- Priority Subgroup

The bits in the Priority Group define the number of priority levels for the purpose of preemption.

The bits in the Priority Subgroup define the number of sub-levels for the purpose of selecting which IRQi will be serviced first if two IRQi are simultaneously pending when the core accepts an interrupt.

### **NVIC PRIORITIES**

The PRIGROUP bits of the AIRCR register are used to configure the division of bits among Priority Group and Subgroup.

AIRCR.PRIGROUP may be written with values in the range of 0..7

On the S7G2, programming PRIGROUP with 0, 1, 2 or 3 has the effect of using the four bits for Priority Group and none for the Subgroup.

For PRIGROUP = 4 the division is 3.1 (3 for Group and 1 for Subgroup)

For PRIGROUP = 5 the division is 2.2, and so on...

These is a partial list of the functions available in CMSIS-CORE that provide access to the NVIC as well as to other interrupt functionality.

Next slides detail these functions

| CMSIS function                                                       | Description                                    |

|----------------------------------------------------------------------|------------------------------------------------|

| <pre>void NVIC_SetPriorityGrouping (uint32_t PriorityGroup)</pre>    | Set priority grouping                          |

| uint32_t NVIC_GetPriorityGrouping (void)                             | Read the priority grouping                     |

| void NVIC_EnableIRQ (IRQn_Type IRQn)                                 | Enable a device-specific interrupt             |

| uint32_t NVIC_GetEnableIRQ (IRQn_Type IRQn)                          | Get a device-specific interrupt enable status. |

| void NVIC_DisableIRQ (IRQn_Type IRQn)                                | Disable a device-specific interrupt            |

| uint32_t NVIC_GetPendingIRQ (IRQn_Type IRQn)                         | Get the pending device-specific interrupt      |

| <pre>void NVIC_SetPendingIRQ (IRQn_Type IRQn)</pre>                  | Set a device-specific interrupt to pending     |

| <pre>void NVIC_ClearPendingIRQ (IRQn_Type IRQn)</pre>                | Clear a device-specific interrupt from pending |

| <pre>uint32_t NVIC_GetActive (IRQn_Type IRQn)</pre>                  | Get the device-specific interrupt active       |

| <pre>void NVIC_SetPriority (IRQn_Type IRQn, uint32_t priority)</pre> | Set the priority for an interrupt              |

| uint32_t NVIC_GetPriority (IRQn_Type IRQn)                           | Get the priority of an interrupt               |

|                                                                      |                                                |

source: infocenter.arm.com

BIG IDEAS FOR EVERY SPACE RENESAS

#### typedef enum {

| /*                    | Cortex-M4 | Process | or E | Exceptions Numbers*/                                                           |         |

|-----------------------|-----------|---------|------|--------------------------------------------------------------------------------|---------|

| Reset_IRQn            | = -15,    | /*!<    | 1    | Reset Vector, invoked on Power up and warm reset                               | */      |

| NonMaskableInt_IRQn   | = -14,    | /*!<    | 2    | Non maskable Interrupt, cannot be stopped or preempted                         | */      |

| HardFault_IRQn        | = -13,    | /*!<    | 3    | Hard Fault, all classes of Fault                                               | */      |

| MemoryManagement_IRQn | = -12,    | /*!<    | 4    | Memory Management, MPU mismatch, including Access Violation and No Match       | * /     |

| BusFault_IRQn         | = -11,    | /*!<    | 5    | Bus Fault, Pre-Fetch-, Memory Access Fault, other address/memory related Fault | ¥<br>*/ |

| UsageFault_IRQn       | = -10,    | /*!<    | 6    | Usage Fault, i.e. Undef Instruction, Illegal State Transition                  | */      |

| SVCall_IRQn           | = -5,     | /*!<    | 11   | System Service Call via SVC instruction                                        | */      |

| DebugMonitor_IRQn     | = -4,     | /*!<    | 12   | Debug Monitor                                                                  | */      |

| PendSV_IRQn           | = -2,     | /*!<    | 14   | Pendable request for system service                                            | */      |

| SysTick_IRQn          | = -1,     | /*!<    | 15   | System Tick Timer                                                              | */      |

| } IRQn_Type;          |           |         |      |                                                                                |         |

This is the IRQn\_Type enumeration defined in file S7G2.h

void \_\_enable\_irq(void)

Resets PRIMASK in the core, allowing interrupts from NVIC to be serviced.

```

Example: ___enable_irq( );

```

void \_\_disable\_irq(void)

Sets PRIMASK in the core, preventing exceptions with configurable priorities (exceptions 4 and up) to be serviced. Example: \_\_disable\_irq();

void NVIC\_EnableIRQ(IRQn\_Type)

Enables (unmask) a specific IRQi line

Example: NVIC Enable(SysTick IRQn);

void NVIC\_DisableIRQ(IRQn\_Type)

Disables (mask) a specific IRQi line

Example: NVIC\_Disable(SysTick\_IRQn);

uint32\_t NVIC\_GetPendingIRQ(IRQn\_Type)

Reads the Pending status (P\_FF) returning 0 (not pending) or 1 (pending)

Example: uint32\_t pend = NVIC\_GetPendingIRQ(SysTick\_IRQn);

void NVIC\_SetPendingIRQ(IRQn\_Type)

Sets the Pending status (P-FF) of a specific IRQi line

Example: NVIC\_SetPendingIRQ(SysTick\_IRQn);

void NVIC\_ClearPendingIRQ (IRQn\_Type) Clears (resets) the Pending status (P-FF) of a specific IRQi line

Example: NVIC\_ClearPendingIRQ(SysTick\_IRQn);

void NVIC\_SetPriority(IRQn\_Type IRQn, uint32\_t priority)

Sets the priority of a specific IRQi line

Example: NVIC SetPriority(SysTick\_IRQn,4);

```

uint32 t NVIC GetPriority(IRQn Type IRQn)

```

Get the priority level of a specific IRQi line

Example: uint32\_t prio = NVIC\_GetPriority(SysTick\_IRQn);

Rem: The integer value of the priority must be in the range of 0 .. 2N-1, where N is the number of priority bits implemented. For S7G2 the range is 0..15.

uint32\_t NVIC\_GetActive(IRQn\_Type)

Reads the Active status (ACTIVE\_FF) returning 0 (not active) or 1 (active)

Example: uint32\_t act = NVIC\_ GetActive (SysTick\_IRQn);